|

Hybrid Solver and Advanced PI Updates

|

Power-aware, high-accuracy SI analysis for leading-edge DDR5 and 112G interfaces, combining advanced interconnect modeling with time-domain simulation for comprehensive SerDes analysis and interface compliance signoff.

|

|

Layout Workbench

|

Offering faster interfaces, customizable themes, context-sensitive menus, and unified workflows, all within a single .spd file for enhanced usability and efficiency.

|

|

Performance-Drive Results

|

Sigrity X allows for significantly faster and more accurate IC package and PCB simulations, with performance enhancements ranging from 7.18X to 15.1X due to distributed computing and code optimization, all without compromising accuracy.

|

|

Signoff Accuracy

|

Catch electrical problems early to deliver on-time, within-budget products using the Sigrity X trusted simulation accuracy and seamlessly leverage electromagnetic (EM) analysis.

|

|

Early Signal and Power Integrity Issue Detection

|

Integration into the efficient and accurate Allegro X design flow with visions identifies signal and power integrity issues early, minimizing analysis and layout iterations and accelerating time to market.

|

|

Operating System Support

|

Multisystem support with Microsoft Windows and Linux

|

|

Interface Databases

|

Interfaces to PCB and IC package layout databases from Cadence, Mentor Graphics, Altium, Zuken, and AutoCAD.

|

|

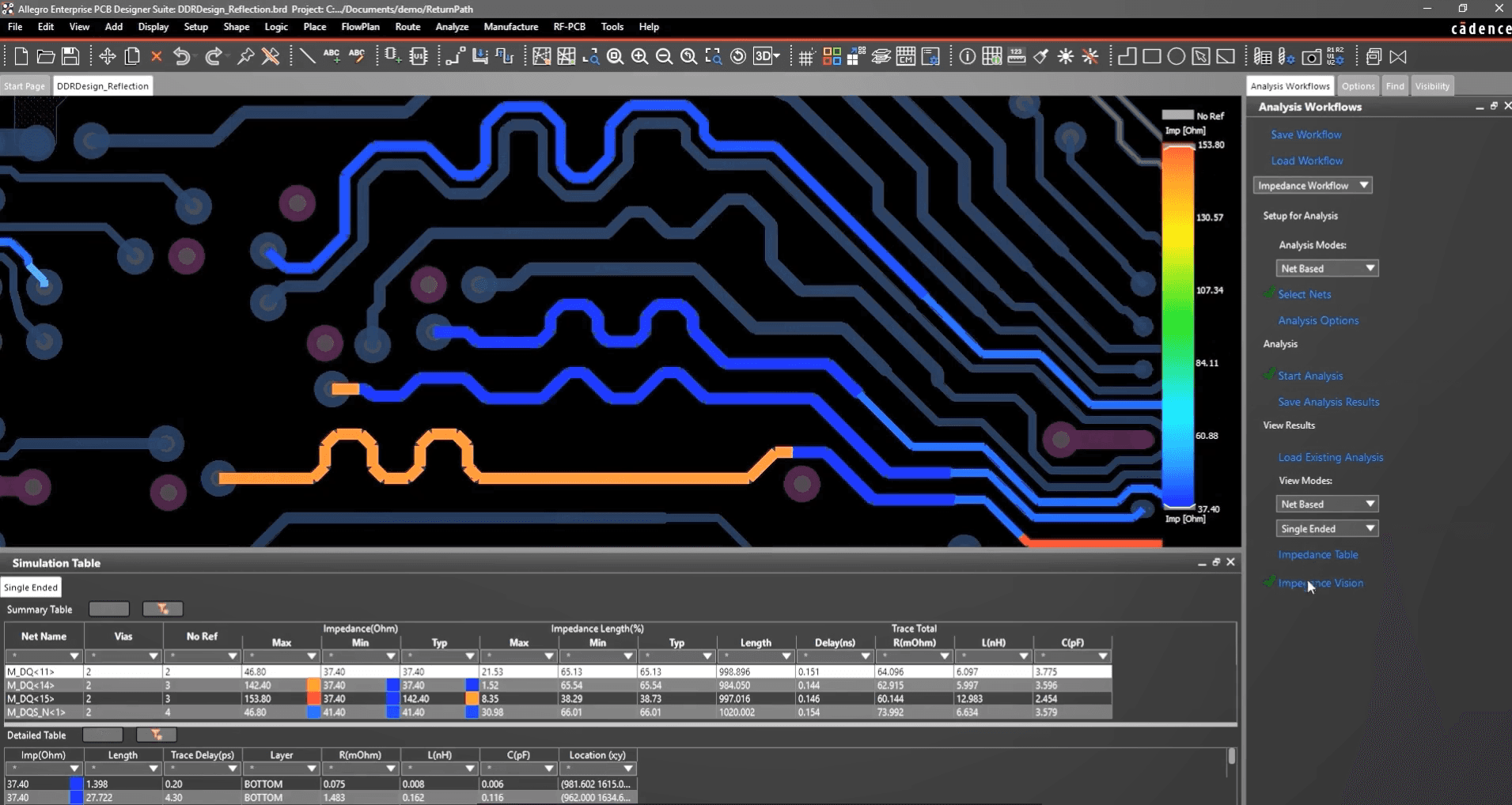

Impedance Analysis Screening

|

The analysis screening feature eliminates the need for SI models, offering a comprehensive global view with intuitive graphic overlays, tables, and plots. Effortlessly sort results to quickly identify and address outliers.

|

|

Coupling Analysis Screening

|

The coupling analysis screening quickly scans the design for cases of excessive coupling between signals. A global view of results is provided with graphics, tables, and plots.

|

|

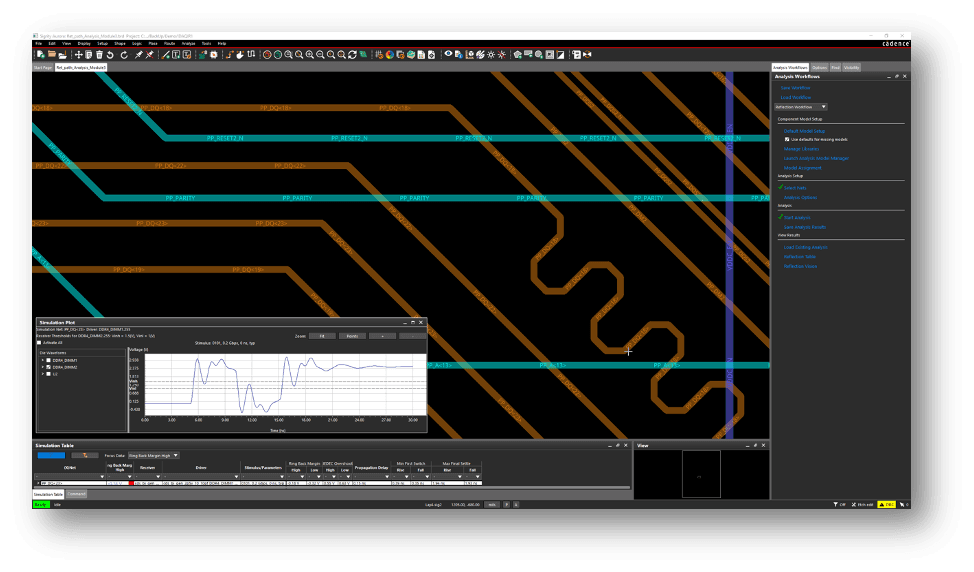

Reflection Analysis

|

Leveraging SI models to simulate selected signals, allowing designers to effortlessly sort and analyze results for outliers across various signal quality metrics. Enjoy enhanced capabilities like detailed waveform viewing, batch simulation, insightful tooltips, and the flexibility to use default or custom I/O models.

|

|

Crosstalk Analysis

|

The crosstalk analysis feature allows designers to use either default or specific I/O models to identify victim crosstalk nets and individual and worst-case aggressors.

|

|

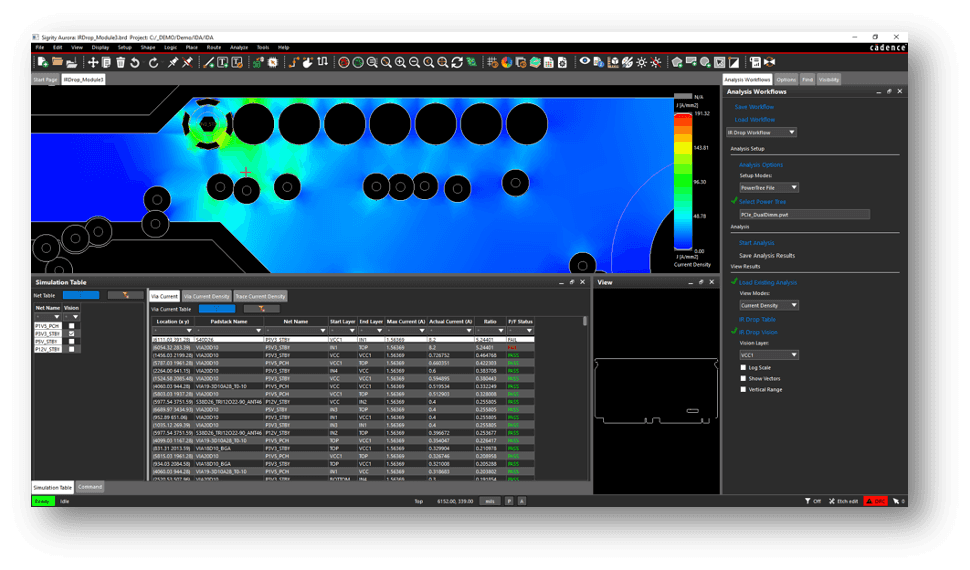

IR Drop Analysis

|

The IR drop analysis feature provides IR drop, absolute voltage, current density, and current view modes. Current vectors, non-deal ground support, and pass/fail constraints are also offered.

|

|

PDN Analysis

|

Accurate handling of non-ideal power delivery system influences on SI

|

|

Comprehensive Evaluation of SI Effects

|

Concurrently evaluate SI effects such as losses, reflections, crosstalk, and simultaneous switching output (SSO).

|

|

Industry Standard File Support

|

SPICE (HSPICE and others), IBIS (native IBIS, BIRD95/98, AMI), S-parameters (Touchstone/Cadence Sigrity Broadband Network Parameter (BNP) syntax), Cadence Sigrity MCP.

|

|

Standard Interface Support

|

Parallel bus interface compliance checks included for DDR2, DDR3, DDR4, LPDDR3, LPDDR4

Serial Link compliance checks included for PCI Express (PCIe) 3.0, PCIe 4.0, SFP+, 10GBASE-KR, HDMI, USB 3.0, USB 3.1, 100BASE-T1

|

|

Automated Die-to-Die Signal Integrity (SI) Analysis

|

Source-synchronous for parallel buses, serial links with a focus on SerDes channels, and a general-purpose topology exploration environment for signal, power, or combined what-if analysis—covering DC to over 56GHz (112Gbps) using frequency domain, time domain, and statistical analysis methods.

|

|

Develop, test, and utilize

|

IBIS AMI TX and RX Model Development and Testing for Serial Link Analysis.

|

|

Reduce costs and time

|

Quantify the bit error rate (BER) and performance of complex SerDes channels.

|

|

Parallel Bus Analysis

|

Supports concurrent simulation of high-speed bus interfaces like DDRx memory designs, accounting for dielectric and conductor losses, reflections, ISI, crosstalk, and SSN, which is crucial for emulating real hardware behavior with tight timing margins and comprehensive analysis across chip, package, and board structures.

|

|

Serial Link Analysis

|

Serial Link Analysis approach simulates end-to-end channel behavior to produce eye diagrams, bathtub curves, and predict BER performance, while identifying jitter and noise impacts for design improvements, fully supporting IBIS AMI TX and RX models in assessing chip-level signal conditioning and clock/data recovery.

|

|

Rapid Model Creation

|

Fast, easy model creation from N-port passive parameters for HSPICE and SPICE simulators.

|

|

High-Fidelity Model Generation

|

Generates models for DC through broadband frequencies with high-order, numerically stable responses, and rigorous passivity enforcement.

|

|

Comprehensive Structural Modeling

|

Models and extracts network parameters for various structures including IC packages, RF components, PCBs, cables, and connectors, addressing real-world scenarios.

|

|

Accurate Model Verification

|

Verifies behavioral model accuracy against the original transistor model with included time domain simulation and accuracy checks during conversion.

|

|

User-Friendly Automation

|

Highly automated, wizard-based approach guides users through creating IBIS-AMI models, including all IBIS BIRD95/BIRD98 power-aware effects.

|

|

Advanced Visualization and Analysis

|

Provides 2D/3D visualization, plotting, and spreadsheet data management to pinpoint package performance issues and potential risks efficiently.

|

|

Comprehensive Interconnect and EMC Analysis

|

Includes interconnect model extraction, TDR, TDT, power ripple analysis, EMC simulation with non-linear driver support, impact assessment of stack-up and plane variations, noise generation observation, system-level power-aware SI analysis, and ESD workflow feedback on TVS diodes effectiveness.

|

|

Comprehensive PDN Optimization and Visualization

|

Eliminates decap over-design for PCBs and IC packages, reduces PDN cost, develops effective decap guidelines, identifies EMI decap locations, and provides intuitive visualization of PDN performance with robust hybrid EM/circuit analysis technology.

|

|

Full-Wave Accuracy

|

Utilizes full-wave hybrid solvers for RLGC parasitics based on S-parameters, accounting for all physical effects and coupling mechanisms, to generate entire package models from a single simulation.

|

|

Comprehensive Package Support

|

Supports various IC package types, including BGA, leadframe, wirebond, and flip-chip for single-die, SiP, and multi-die designs. Extracts models for entire packages or selected nets, incorporating discrete components for accurate power delivery and coupling analysis, crucial for SSO/SSN analysis.

|

Product Details

Product Details

Success Cases

Success Cases