Key Features

➤By identifying potential issues before and after wiring as early as possible, design costs can be reduced and design time can be shortened

➤Ensure reliable power distribution by verifying AC, DC, and power ripple analysis

➤Optimize PDN on the entire PCB circuit board/packaging interface

➤Using a module based schematic editor to easily solve system level power analysis problems

Product Details

Product Details

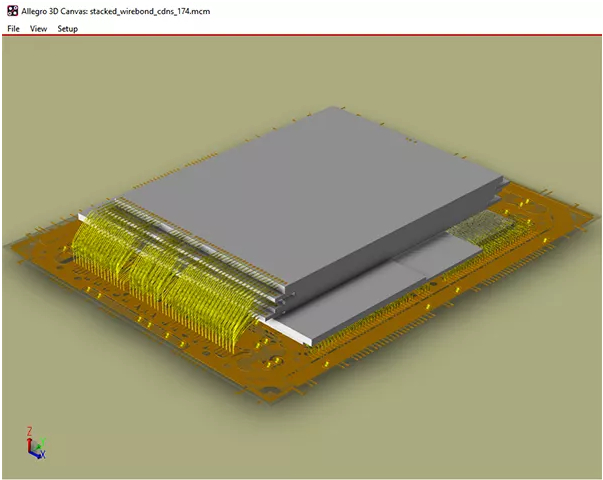

Assist you in quickly verifying the adequacy, effectiveness, and stability of the Power Distribution Network (PDN), Cadence ® Sigrity ™ Advanced PI enables power integrity (PI) experts to perform PDN simulation verification from each power source of each receiver across multiple circuit boards and packages.

Cadence Allegro ® PowerTree ™ Technology enables you to analyze and validate the bill of materials defined during the logical design phase before the physical design begins. With the advancement of physical implementation, you can reuse PowerTree settings to make DC and AC power integrity analysis in various design stages a one click process.

DC analysis that takes into account thermal effects

Sigrity PowerDC ™ Technology provides effective DC analysis for the approval process of IC packaging and PCB design, including electrical/thermal co simulation, to maximize accuracy. Sigrity PowerDC technology can quickly and accurately locate areas with excessive IR voltage drop, as well as areas with high current density and hot spots with high temperature, minimizing the risk of design failure to the greatest extent possible.

AC analysis

Sigrity OptimizePI ™ Technology can perform complete AC analysis on PCB circuit boards and IC packaging. This technology supports research before and after wiring to quickly locate the optimal decoupling capacitor selection and placement, thereby meeting your PDN needs at the lowest possible cost. Check the PDN impedance curve based on the target impedance constraint conditions to ensure that the design complies with the PDN specifications.

Power Ripple Analysis

Sigrity SPEED2000 ™ The simulation analysis process of power ground noise coupling in technology can be used for direct time-domain power/ground noise simulation of I/O power supplies. Sigrity Advanced PI provides a direct time-domain power integrity simulation method for PCB or IC packaging, without the need to extract S-parameter models and use them in SPICE simulations. This method provides stable simulation results and is more time-saving than other methods.

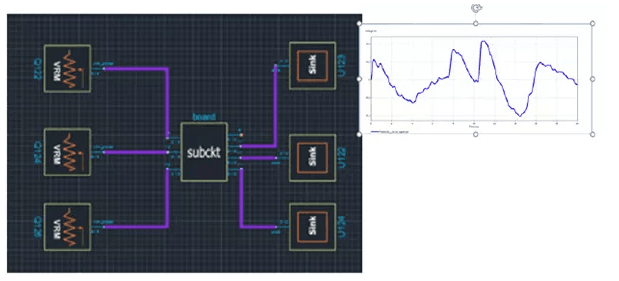

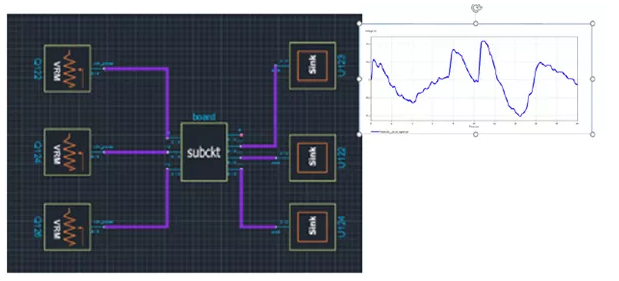

Sigrity Topology Explorer

A universal topology exploration function that can be used to explore power topologies in multiple system designs. You can create and simulate a complete "power receiver" connection by connecting power ports to multiple chips, packages, and circuit boards. Through the Voltage Regulator Module (VRM) model, Sigrity PowerSI can be used ™ Or Cadence Clarity ™ 3D Solver creates PDN models for each structure to add stimuli. At every critical point from the power supply to the receiving end, the PDN voltage can be presented through an intuitive time-domain view. You can determine if any part of the PDN is causing a power shortage issue within the system specifications.

The Sigrity Topology Explorer interface is intuitive, allowing you to easily connect PDN interconnect models across multiple circuit boards, chips, and packages, and view their impact on power stability.

PRODUCT FUNCTION

➤ Automatically set up DC simulation using PowerTree data (power/receiver definitions) extracted during the schematic design phase Success Cases

Success Cases